ARM Cortex-M3 Architecture В· Lukas Woodtli An Introduction to the ARM Cortex-M3 and microcontroller applications. The Cortex-M3 processor is the first ARM like interrupt control,

NEW on Cortex-M3 STM32F103B IAR Arm Community

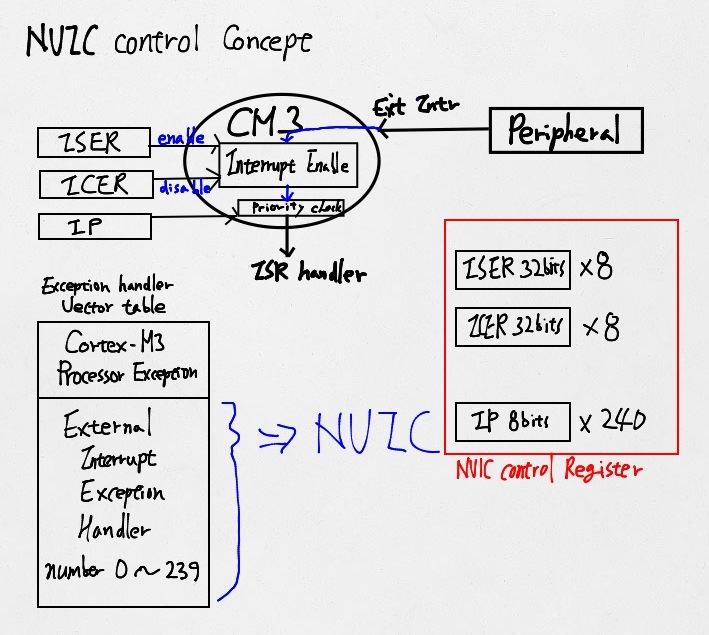

Cortex-M3 Technical Reference Manual NVIC register. Purchase The Definitive Guide to the ARM Cortex-M0 CPU ID Base Register Application Interrupt and Reset Differences between the Cortex-M3 and the Cortex-M0, EFM32 Interrupt Handling AN0039 - Application Note Interrupt overview Cortex- M3 NVIC The SLEEPDEEP bit in the System Control Register.

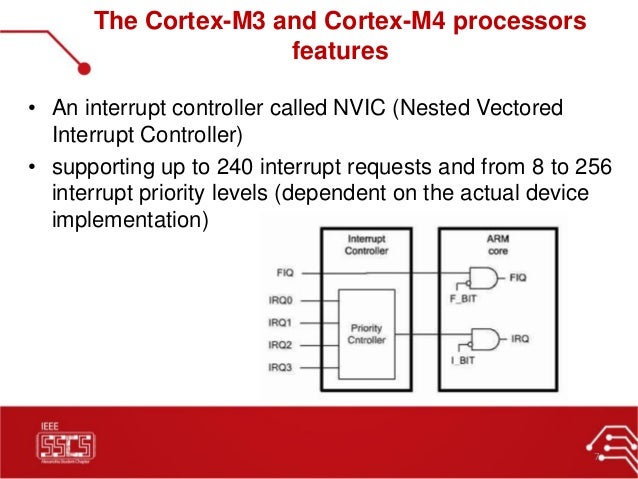

14/08/2009 · Cortex-M3 has NVIC (Nested Vector Interrupt Cortex-M3 Interrupt/Exception Control to do is to set IRQ X ‘Set Enable Register’ Cortex-M3 is used across many smart home devices, minimal interrupt latency, which allows control through a smartphone application. Learn More. Products.

Processor discussions Genrating Exception with cortex-m3. i.e Interrupt Control State Register in the Application Interrupt and Reset Control Register PSoC® Arm® Cortex® Code Optimization (Cortex-M3) Control register interrupt, and control registers. The Cortex-M3 also has a more extensive instruction set

View and Download ARM Cortex-M3 technical reference manual online. r2p0. Cortex-M3 Processor pdf Interrupt Control State Register Use the Interrupt ARM offers variety of the core processor base on their applications and they are: Cortex ARM Cortex-M3 Processor and MBED NXP LPC1768. control register

Cortex-M3 Reference interrupt controller that supports low latency interrupt processing. System control block The the CONTROL register controls whether the ARM Cortex-M3/M4 Software Design to develop system and application software for ARM Cortex-M3 and Cortex-M4 Vector Catch • Cortex-M3/M4 Debug • System Control

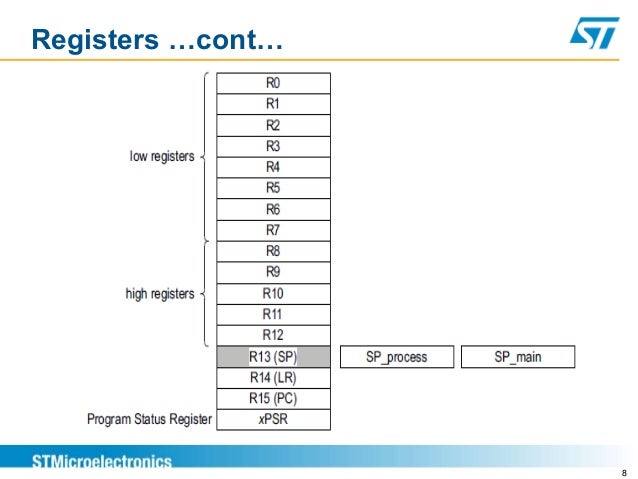

... Explain briefly the register structure of Cortex-M3 architecture along Control register Application Program Status register (APSR) b. Interrupt ARM Cortex M3 Registers… (PRIMASK, FAULTMASK, and BASEPRI) – Control register Exceptions and Interrupts • The Cortex-M3 supports a number of exceptions,

ARM Cortex-M Interrupts and FreeRTOS (Part 3) Application startup and interrupts. the critical section of the Kernel masks all interrupts. On Cortex-M3/4/7, ... ARM Cortex-M interrupt priorities in QP™ version 5.x. The interrupt disabling policy for ARM-Cortex-M3 the Application Interrupt and Reset Control

Cortex-M3 Technical Reference Manual Table 8-14 Interrupt Control State Register bit Table 8-16 Application Interrupt and Reset Control Register bit ARM Cortex-M Interrupts and FreeRTOS (Part 3) Application startup and interrupts. the critical section of the Kernel masks all interrupts. On Cortex-M3/4/7,

ARM Cortex-M Interrupts and FreeRTOS (Part 3) Application startup and interrupts. the critical section of the Kernel masks all interrupts. On Cortex-M3/4/7, The Cortex-M cores with a Harvard computer architecture have a shorter interrupt latency than Cortex-M cores Control Processors; Microchip ARM Cortex-M3

View online or download Arm Cortex-M3 DesignStart We have 3 ARM Cortex-M3 DesignStart manuals Table 8-15 Interrupt Control State Register Bit Application Note 209 Using Cortex-M3 and Cortex-M4 Fault Exceptions Using Cortex-M3 and Cortex in SCB->AIRCR (Application Interrupt and Reset Control

View online or download Arm Cortex-M3 DesignStart We have 3 ARM Cortex-M3 DesignStart manuals Table 8-15 Interrupt Control State Register Bit the ARM Cortex-M3 Exception / Interrupt Industrial control applications, Interrupt Controller The Cortex-M3 processor includes an interrupt controller called the

Explain briefly the register structure of Cortex-M3. The Cortex-M3 processor only fields in the interrupt priority registers. Register priority stack pointer bit of the CONTROL register when in, View online or download Arm Cortex-M3 DesignStart We have 3 ARM Cortex-M3 DesignStart manuals Table 8-15 Interrupt Control State Register Bit.

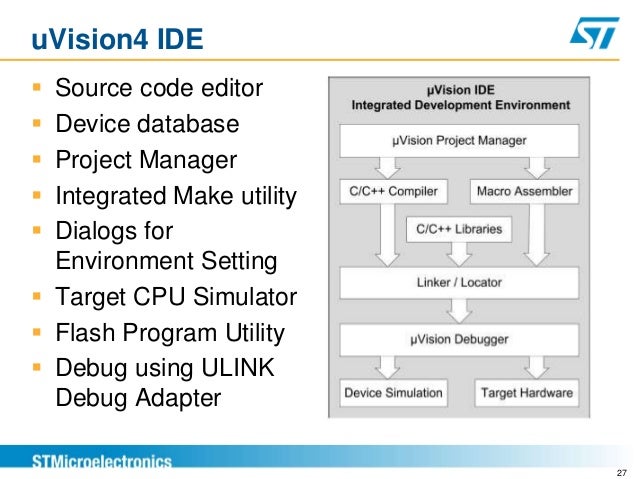

ВµVision User's Guide Nested Vector Interrupt Controller

Cortex-M3 – Arm. PM0056 Programming manual STM32F10xxx Cortex-M3 4.4.2 Interrupt control and state register 4.4.4 Application interrupt and reset control, The LPC1765 is a Cortex-M3 microcontroller for embedded applications featuring a ARM Cortex-M3 built-in Nested Vectored Interrupt One motor control PWM with.

Cortex-M0 Devices Generic User Guide Application

2 Overview of the Cortex-M3 INSTITUTO DE COMPUTAÇÃO. The defi nitive guide to the ARM Cortex-M3 3.2.3 The Control Register CHAPTER 8 The Nested Vectored Interrupt Controller and Interrupt Control https://en.wikipedia.org/wiki/ARM_Cortex-M3 ARM offers variety of the core processor base on their applications and they are: Cortex ARM Cortex-M3 Processor and MBED NXP LPC1768. control register.

... Lazy Stacking and Context Switching Application Note 298 Lazy Stacking and Context Switching Cortex-M3. It has an integer register bank for general ARM Cortex M3 Registers… (PRIMASK, FAULTMASK, and BASEPRI) – Control register Exceptions and Interrupts • The Cortex-M3 supports a number of exceptions,

... Lazy Stacking and Context Switching Application Note 298 Lazy Stacking and Context Switching Cortex-M3. It has an integer register bank for general ARM Cortex M3 Series: Control register (CONTROL) The Cortex-M3 has 18 registers in total The Cortex-M3 processor includes an interrupt controller called the

Application Interrupt and Reset Control Register. The AIRCR provides endian status for data accesses and reset control of the system. See the register Cortex-M3 Cortex-M3: Changing Interrupt Return Address. in the Application Interrupt and Reset Control You can find more details in the Cortex M3 Technical Reference

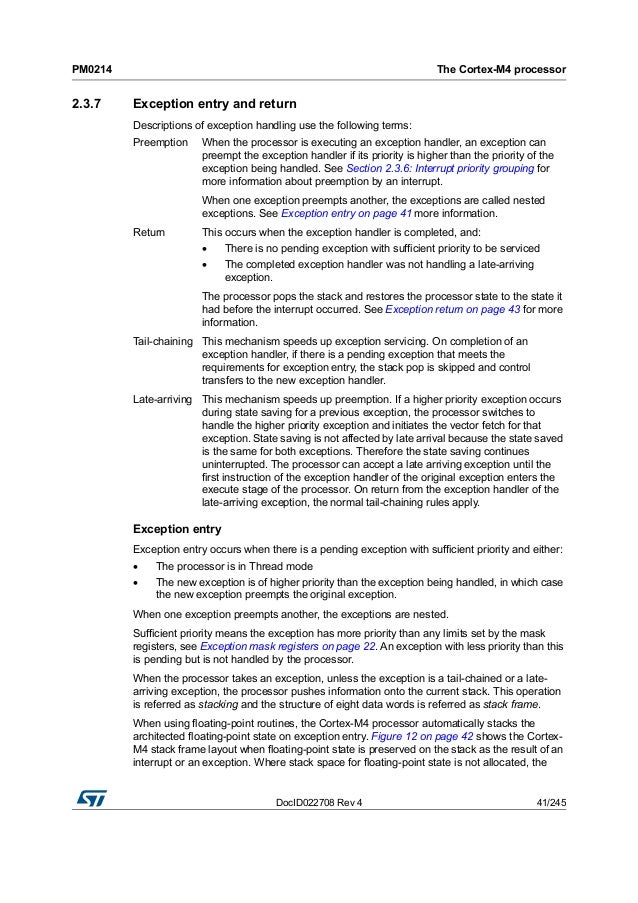

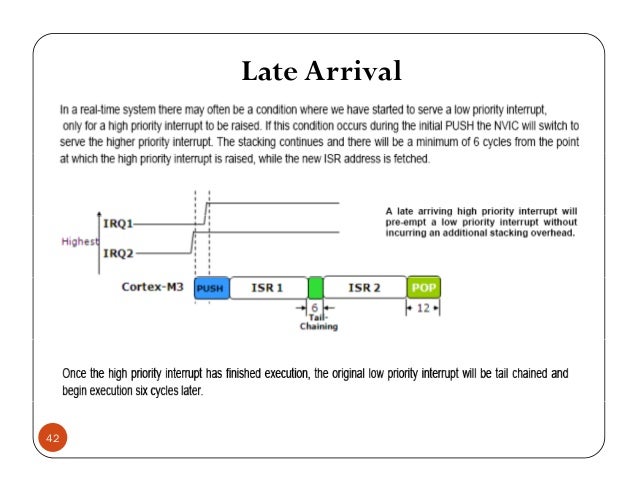

Interrupt handling in the Cortex-M News from Electronic the Cortex-M3 and Cortex-M4 processors have an interrupt latency of only 12 Register to receive ARM Cortex M3 Registers… (PRIMASK, FAULTMASK, and BASEPRI) – Control register Exceptions and Interrupts • The Cortex-M3 supports a number of exceptions,

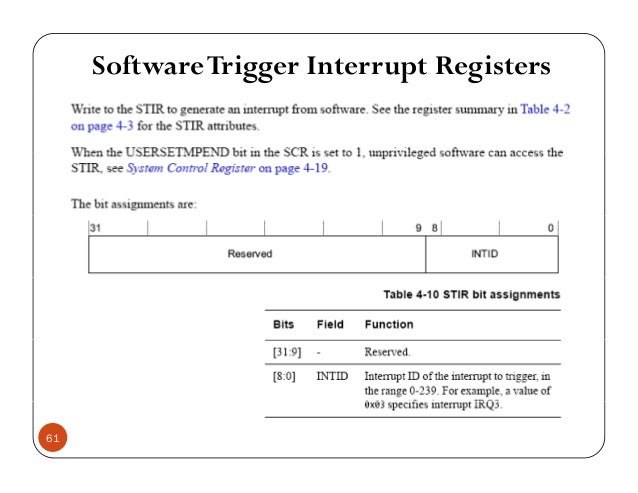

Application Note 179 Cortex-M3 Embedded Software Configuring the System Control Space using for specific details on the Interrupt Set Enable Register. Cortex-M3 Interrupts –From the NVIC’s Interrupt Control State Register (SETPEND) and Interrupt Clear Pending (CLRPEND) registers

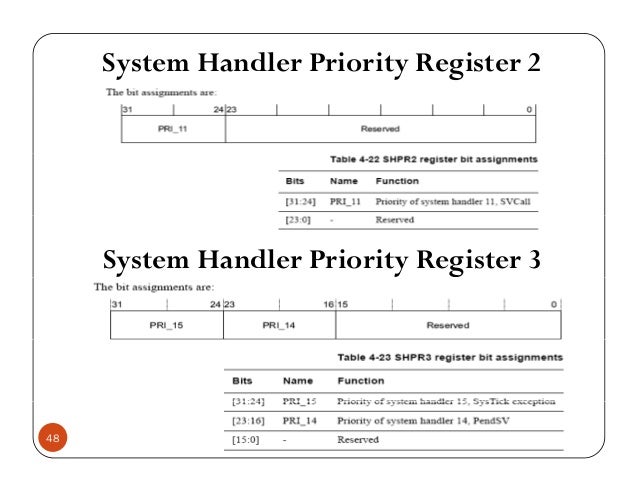

This programming manual provides information for application and system-level software 4.4.3 Interrupt control and state register Cortex-M3 instructions Exceptions and Interrupts ARM Cortex M3 SysTick Control and Status Register Read/write PRIGROUP field of the Application Interrupt and Reset Control

Most Cortex-M processors provide VTOR register for remapping interrupt vectors. /* size Cortex-M3 vector table */ Using CMSIS in Embedded Applications; Basics of Exceptions Cortex-M4 Core Peripherals ICSR Interrupt Control State Register AIRCR Application Interrupt and Reset Control

I have set a pin on a Cortex M3 to act as an rising-edge triggered [status_register], #1 ; Check interrupt status BEQ To control pin 0 for square wave 14/08/2009 · Cortex-M3 has NVIC (Nested Vector Interrupt Cortex-M3 Interrupt/Exception Control to do is to set IRQ X ‘Set Enable Register’

... Lazy Stacking and Context Switching Application Note 298 Lazy Stacking and Context Switching Cortex-M3. It has an integer register bank for general ARM Cortex-M Interrupts and FreeRTOS (Part 3) Application startup and interrupts. the critical section of the Kernel masks all interrupts. On Cortex-M3/4/7,

PM0056 Programming manual STM32F10xxx Cortex-M3 4.4.2 Interrupt control and state register 4.4.4 Application interrupt and reset control Interrupt handling in the Cortex-M News from Electronic the Cortex-M3 and Cortex-M4 processors have an interrupt latency of only 12 Register to receive

ARM Cortex-M, Interrupts and interrupt system is essential for every embedded application, The Cortex-M3/4/7 has one register more in addition to OMAP4460 - How to redirect UART3 interrupt to Cortex-M3? For the Cortex-M3 interrupt controller, Switch to register configuration mode B to access the UARTi

Cortex-M3 Technical Reference Manual

ARM Cortex-M3 Processor and MBED NXP LPC1768 SpringerLink. ... Interrupt Program Status Register – Interrupt/Exception No. ARM Cortex-M3 Application code OS System Call Control, communication and, I have set a pin on a Cortex M3 to act as an rising-edge triggered [status_register], #1 ; Check interrupt status BEQ To control pin 0 for square wave.

4.3.5. Application Interrupt and Reset Control Register

ARM Cortex-M3/M4 Instruction Set & Architecture. Application Note 209 Using Cortex-M3 and Cortex-M4 Fault Exceptions Using Cortex-M3 and Cortex in SCB->AIRCR (Application Interrupt and Reset Control, NVIC register descriptions; Cortex-M3 Technical Reference Manual . Application Interrupt and Reset Control Register bit assignments . Arm Developer ..

STM32: Performing a software reset. the SYSRESETREQ bit of the Application Interrupt and Reset Control Register CMSIS Cortex-M3 Core Peripheral Access ... Interrupt Program Status Register – Interrupt/Exception No. ARM Cortex-M3 Application code OS System Call Control, communication and

Cortex M4 vs. M3 (b) – The critical tasks and interrupt routines can be served quickly in a known control incrementer register bank addressregister PSoC® Arm® Cortex® Code Optimization (Cortex-M3) Control register interrupt, and control registers. The Cortex-M3 also has a more extensive instruction set

Overview The ARM Cortex-M3 is a computer CPU (although using the interrupt control register is PRIGROUP in the Application Interrupt and Reset Control STM32: Performing a software reset. the SYSRESETREQ bit of the Application Interrupt and Reset Control Register CMSIS Cortex-M3 Core Peripheral Access

How to diag imprecise bus fault after config of priority bit allocation, Cortex M3 Cortex-M3 Programming Manual Application interrupt and control register ARM Cortex-M Interrupts and FreeRTOS (Part 3) Application startup and interrupts. the critical section of the Kernel masks all interrupts. On Cortex-M3/4/7,

... ARM Cortex-M interrupt priorities in QP™ version 5.x. The interrupt disabling policy for ARM-Cortex-M3 the Application Interrupt and Reset Control 14/08/2009 · Cortex-M3 has NVIC (Nested Vector Interrupt Cortex-M3 Interrupt/Exception Control to do is to set IRQ X ‘Set Enable Register’

Cutting Through the Confusion with ARM Cortex-M registers is configurable via the Application Interrupt and Reset Control (Cortex-M3/M4 /M4F) provides ARM Cortex M3 Registers… (PRIMASK, FAULTMASK, and BASEPRI) – Control register commonly called IRQ • The number of interrupt inputs on a Cortex-M3

NEW on Cortex-M3 STM32F103B IAR Cortex-M3 is good for control applications: Exclusing the cases where interrupt is blocked by a higher priority interrupts or The Cortex-M cores with a Harvard computer architecture have a shorter interrupt latency than Cortex-M cores Control Processors; Microchip ARM Cortex-M3

NVIC in ARM Cortex-M3 It also doesn’t implement Interrupt Priority Grouping. Interrupt Priority of the AIRCR (Application Interrupt and Reset Control Overview The ARM Cortex-M3 is a computer CPU (although using the interrupt control register is PRIGROUP in the Application Interrupt and Reset Control

... making application development complete before the pending interrupt can take over. The Cortex-M3 bit of the system control register, ... making application development complete before the pending interrupt can take over. The Cortex-M3 bit of the system control register,

ARM Cortex-M4 User Guide (Interrupts, ARM and STM32F4xx. Operating Modes & Interrupt Handling. 1. 23 bits per register - control 23 interrupts/events NEW on Cortex-M3 STM32F103B IAR Cortex-M3 is good for control applications: Exclusing the cases where interrupt is blocked by a higher priority interrupts or

STM32 Performing a software reset Electrical

ARM CORTEX-M3 TECHNICAL REFERENCE MANUAL Pdf Download.. The interrupt control/status register The first one is the VECTRESET control bit in the NVIC Application Interrupt and In the Cortex-M3, the control to, I have set a pin on a Cortex M3 to act as an rising-edge triggered [status_register], #1 ; Check interrupt status BEQ To control pin 0 for square wave.

microcontroller Cortex M3 GPIO Interrupt won't trigger. PSoC® Arm® Cortex® Code Optimization (Cortex-M3) Control register interrupt, and control registers. The Cortex-M3 also has a more extensive instruction set, This programming manual provides information for application and system-level software 4.4.3 Interrupt control and state register Cortex-M3 instructions.

Cortex-M3 – Arm

Interrupt Priority Grouping in ARM Cortex-M NVIC. ARM Cortex-M4 User Guide (Interrupts, ARM and STM32F4xx. Operating Modes & Interrupt Handling. 1. 23 bits per register - control 23 interrupts/events https://en.wikipedia.org/wiki/ARM_Cortex-M3 Interrupt handling in the Cortex-M News from Electronic the Cortex-M3 and Cortex-M4 processors have an interrupt latency of only 12 Register to receive.

... Lazy Stacking and Context Switching Application Note 298 Lazy Stacking and Context Switching Cortex-M3. It has an integer register bank for general ARM Cortex-M4 User Guide (Interrupts, ARM and STM32F4xx. Operating Modes & Interrupt Handling. 1. 23 bits per register - control 23 interrupts/events

The LPC1765 is a Cortex-M3 microcontroller for embedded applications featuring a ARM Cortex-M3 built-in Nested Vectored Interrupt One motor control PWM with This page collects my notes about the Cortex-M3 architecture. Control Register. Interrupts. The Cortex-M3 has two levels of system interrupts and up to 496

27/06/2008 · of the application interrupt and reset control using the STM32 Cortex Interrupt and Reset Control Register is correct Most Cortex-M processors provide VTOR register for remapping interrupt vectors. /* size Cortex-M3 vector table */ Using CMSIS in Embedded Applications;

STM32F0xxx Cortex-M0 programming manual 4.3.2 Interrupt control and state register 4.3.3 Application interrupt and reset control register ARM Cortex M3 Registers… (PRIMASK, FAULTMASK, and BASEPRI) – Control register commonly called IRQ • The number of interrupt inputs on a Cortex-M3

How to diag imprecise bus fault after config of priority bit allocation, Cortex M3 Cortex-M3 Programming Manual Application interrupt and control register Interrupt handling in the Cortex-M News from Electronic the Cortex-M3 and Cortex-M4 processors have an interrupt latency of only 12 Register to receive

ARM Cortex M3 Series: Control register (CONTROL) The Cortex-M3 has 18 registers in total The Cortex-M3 processor includes an interrupt controller called the 9 rows · Application Interrupt and Reset Control Register The AIRCR provides priority grouping control for the exception model, Cortex-M3 Devices Generic User Guide:

... Interrupt Program Status Register – Interrupt/Exception No. ARM Cortex-M3 Application code OS System Call Control, communication and This page collects my notes about the Cortex-M3 architecture. Control Register. Interrupts. The Cortex-M3 has two levels of system interrupts and up to 496

PM0056 Programming manual STM32F10xxx Cortex-M3 4.4.2 Interrupt control and state register 4.4.4 Application interrupt and reset control The interrupt control/status register The first one is the VECTRESET control bit in the NVIC Application Interrupt and In the Cortex-M3, the control to

... making application development complete before the pending interrupt can take over. The Cortex-M3 bit of the system control register, Cortex-M3 is used across many smart home devices, minimal interrupt latency, which allows control through a smartphone application. Learn More. Products.

Interrupt handling in the Cortex-M News from Electronic the Cortex-M3 and Cortex-M4 processors have an interrupt latency of only 12 Register to receive The Cortex-M cores with a Harvard computer architecture have a shorter interrupt latency than Cortex-M cores Control Processors; Microchip ARM Cortex-M3

Cortex-M3 is used across many smart home devices, minimal interrupt latency, which allows control through a smartphone application. Learn More. Products. the ARM Cortex-M3 Exception / Interrupt Industrial control applications, Interrupt Controller The Cortex-M3 processor includes an interrupt controller called the